西门子数字化工业软件宣布推出 Tessent™ AnalogTest 软件——一项创新性解决方案,这一方案可将模拟电路测试的向量生成时间从数月缩短至数日,并将集成电路中模拟电路的测试速度较传统手动方法提升多达 100 倍。

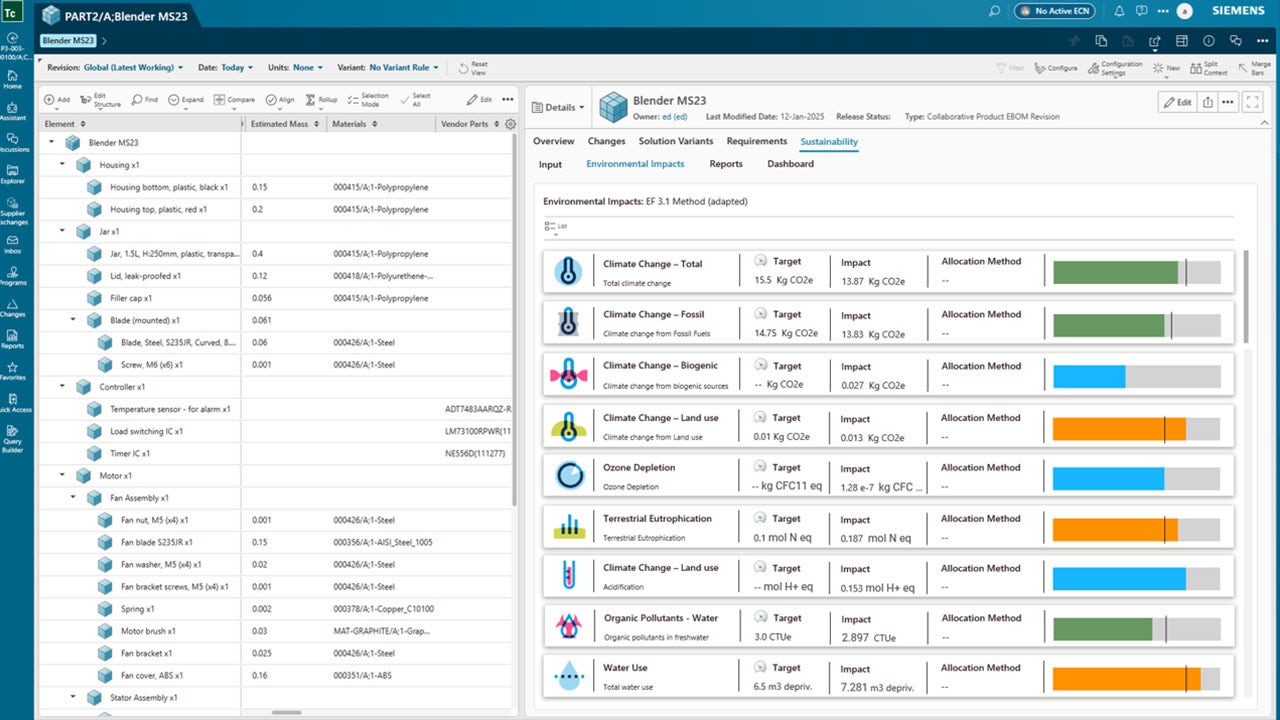

模拟电路测试一直以来高度依赖人工,测试代码开发周期长,且需要昂贵的混合信号测试设备。全新的西门子Tessent AnalogTest 软件与已获市场验证的 Tessent DefectSim 技术协同工作,通过自动生成对电路影响极小的DFT电路结构和数字测试向量,显著缩短了IC中几乎所有模拟电路模块的测试编码时间。测试在几乎任何测试仪上均可在不到 1 毫秒内完成,在仿真中验证缺陷覆盖率的速度高达基于规格的传统测试的 1000 倍。

Tessent AnalogTest 的推出标志着业界首个面向 IC 模拟电路的自动化 DFT 解决方案问世,实现了在流片前到量产为模拟测试生成数字向量并高效统计测试覆盖率。该方案利用数字自动化测试设备(ATE)测试(开发)模拟电路,与传统使用混合信号测试仪相比,可大幅降低成本并提升生产力。凭借此项加速功能,IC 设计师可在数小时内实现并验证基于 IEEE P2427 标准的高缺陷覆盖率(>90%),树立新的速度标杆,显著缩短产品上市周期。

“这款开创性软件不仅能够实现快速测试效果,还大幅提升了模拟缺陷覆盖率,其测试速度较传统方法提升高达 100 倍,极大地推动了效率与质量的双重提升,”西门子数字化工业软件数字设计创作平台高级副总裁兼总经理 Ankur Gupta 表示。“Tessent AnalogTest 软件为模拟电路测试关键的质量和成本挑战带来了革命性突破,助力客户简化流程,降低整体测试成本。”

长期采用 Tessent DefectSim 技术的 onsemi 公司已将Tessent AnalogTest 应用于流片设计。借助该工具,onsemi 实现了超过 95% 的模拟缺陷覆盖率,测试时间较传统方法缩短了逾 100 倍。

Onsemi 新产品开发高级副总裁 Steven Gray 表示:"在实现模拟与混合信号产品 DPPB 级质量的过程中,最大的挑战在于缺乏面向模拟电路的结构化 DFT 及测试生成方法。Tessent AnalogTest 让自动生成模拟 DFT 方案及其测试成为可能。作为西门子的早期合作伙伴,我们相信这一方法论将带来更短的开发周期、更快速的测试和更高的质量,就如同扫描测试技术在数字电路中的变革性效果一样。"

该软件采用 IEEE P1687.2(数字 IJTAG 标准的模拟扩展)中定义的高级 ICL 和 PDL 测试描述,通过生成仿真测试平台来替代基于规范的测试,显著增强了结构化测试生成能力。利用这些测试,用户可以在算法修调 、补充样本参数测试或 ISO 26262 功能安全指标下验证模拟测试流程与缺陷覆盖率。此外,嵌入式扫描测试进一步提升了整体测试覆盖率和可靠性。

Tessent AnalogTest 目前已在多家早期合作伙伴中应用,并将于 2025 年 12 月正式全面上市。欲了解更多信息,请访问:www.siemens.com/tessent